Extras

Summary of the Extra components in Schematic Editor

These Signal Processing components focus on conversions, transformations, and other numerical operations that may be necessary for the model. Miscellaneous controller components that are not in other categories are also included here. Their descriptions and supported features are given in Table 1.

| Component | Description | Features | Help file | ||

|---|---|---|---|---|---|

| Supported input types | Supported output types | Vector support | |||

abc to alpha beta |

Transformation from three-phase (abc) signal to alpha-beta-gamma reference frame | real, int, uint | real | no | ABC to Alpha Beta |

abc to dq |

Transformation from three-phase (abc) signal to dq0 rotating reference frame | real, int, uint | real | no | ABC to DQ |

alpha beta to abc |

Transformation from alpha-beta-gamma reference frame to three-phase (abc) signal | real, int, uint | real | no | Alpha Beta to ABC |

alpha beta to dq |

Transformation from alpha-beta reference frame to dq reference frame | real, int, uint | real | no | Alpha Beta to DQ |

Counter |

Counter with enable and edge or level sensitive reset | real, int, uint | real, int, uint | no | Counter |

D Flip Flop |

Tracks the Boolean value on its input and updates its output according to the clock signal. | real, int, uint | real, int, uint | yes | D Flip Flop |

dq to abc |

Transformation from dq0 rotating reference frame to three-phase (abc) | real, int, uint | real | no | DQ to ABC |

dq to alpha beta |

Transformation from dq reference frame to alpha-beta reference frame | real, int, uint | real | no | DQ to Alpha Beta |

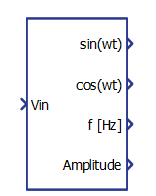

FLL Sync |

Frequency-locked Loop algorithm for grid synchronization | real | real | yes | FLL Sync |

FMU import |

Adds support for FMU file import | real, int, uint | real, int, uint | no | FMU Import |

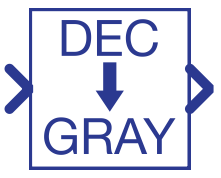

Gray Coder |

Converts inputted unsigned integer value to Gray code |

real, int, uint | real, int, uint | no | Gray Coder |

JK Flip Flop |

Implements JK Flip Flop sequential logic | real, int, uint | real, int, uint | yes | JK Flip Flop |

Kalman Filter Sync |

Generates an output signal whose phase is related to the phase of an input signal and another signal with a 90 degree phase difference. | real | real | no | Kalman Filter Synchronization |

Mean Value |

Computes mean value of an input signal | real | real | no | Mean Value |

PID Controller |

Discrete-time PID control with optional anti-windup feature | real, int, uint | real | no | PID Controller |

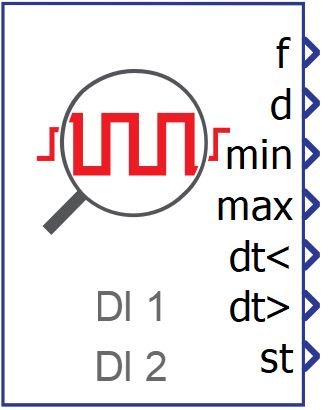

PWM Analyzer |

Extracts features of PWM signals at specified digital inputs. | - | real, int | yes | PWM Analyzer |

PWM Modulator |

Multi-channel PWM modulator with a symmetrical triangular carrier and dead time generator | real, int, uint | - | no | PWM modulator |

RMS Value |

Computes RMS value of an AC signal | real | real | no | RMS Value |

Sample and Hold |

Samples an input signal each time a trigger event is detected. | real, int, uint | real, int, uint | yes | Sample and Hold |

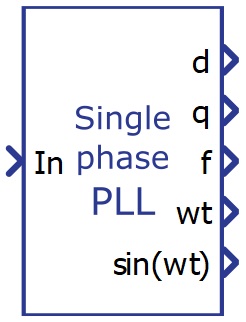

Single Phase PLL |

Single Phase PLL component based on SOGI | real | real | no | Single Phase PLL |

SR Flip Flop |

Implements SR Flip Flop sequential logic. | real, int, uint | real, int, uint | yes | SR Flip Flop |

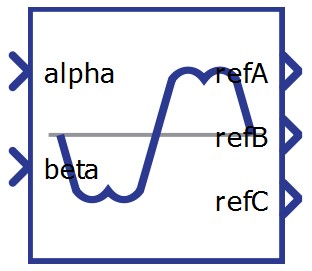

SVPWM References Generator |

Generates PWM reference signals for three-phase two-level inverters using the space-vector pulse width modulation (SVPWM) technique. | real | real | no | SVPWM (Space Vector Pulse Width Modulation) reference generator |

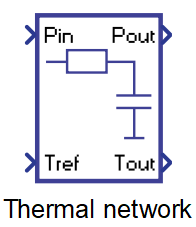

Thermal Network |

Implements a signal processing model of a thermal system that can be parametrized with either Cauer or Foster thermal model data. | real | real | yes | Thermal network |

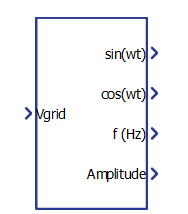

Three Phase PLL |

Generates output signals whose phase is related to the phase of a three-phase signal input. | real | real | no | Three phase PLL |