Is there a need for circuit partitioning

This section describes how to determine if there is a real need for circuit partitioning or some other solution, such as changing your HIL configuration, should be considered.

- There are too many converters in the circuit - the overall weight of the converters exceeds the limit

- There are too many contactors in the circuit - the overall number of contactors exceeds the limit

- Matrix memory overloaded - most commonly due to a large number of switches in the circut

- The simulation time step is too big

A complementary demonstration of practical cases where we need to consider these resource limits is also available in the Video Knowledgebase and as part of the HIL Fundamentals course.

Too many converters in the circuit

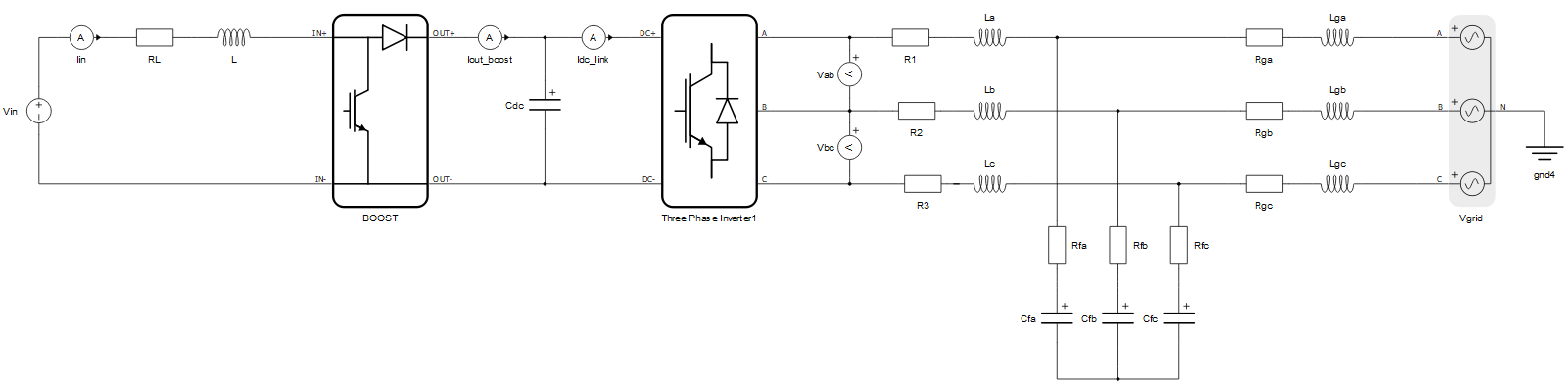

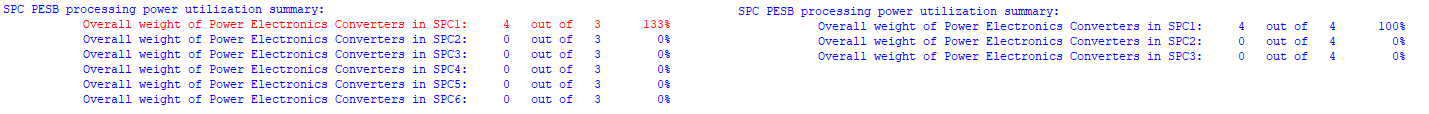

One of the most common reasons to perform circuit partitioning is there are too many converters in the model. Converters are characterized by their weight. Processing cores usually support converters up to weight 3 (for example a three phase converter), but there are some processor configurations that support converters up to weight 4, such as HIL604 in Configuration 4, or C4. In the example model shown in Figure 1, a boost converter (weight = 1) and a three phase converter (weight = 3) are present. This means that the overall weight of power electronic converters is 4. If this circuit is compiled for HIL604 C1, the compiler will report an error that the overall weight of converters exceeds the limit. While at first glance it seems that we cannot avoid circuit partitioning into two cores, we could instead switch to HIL604 C4 to solve this issue without the need of circuit partitioning. In some cases it is better to change the configuration than to partition the circuit. The compiler report for the same model, compiled for both HIL604 C1 and HIL604 C4 is shown in Figure 2.

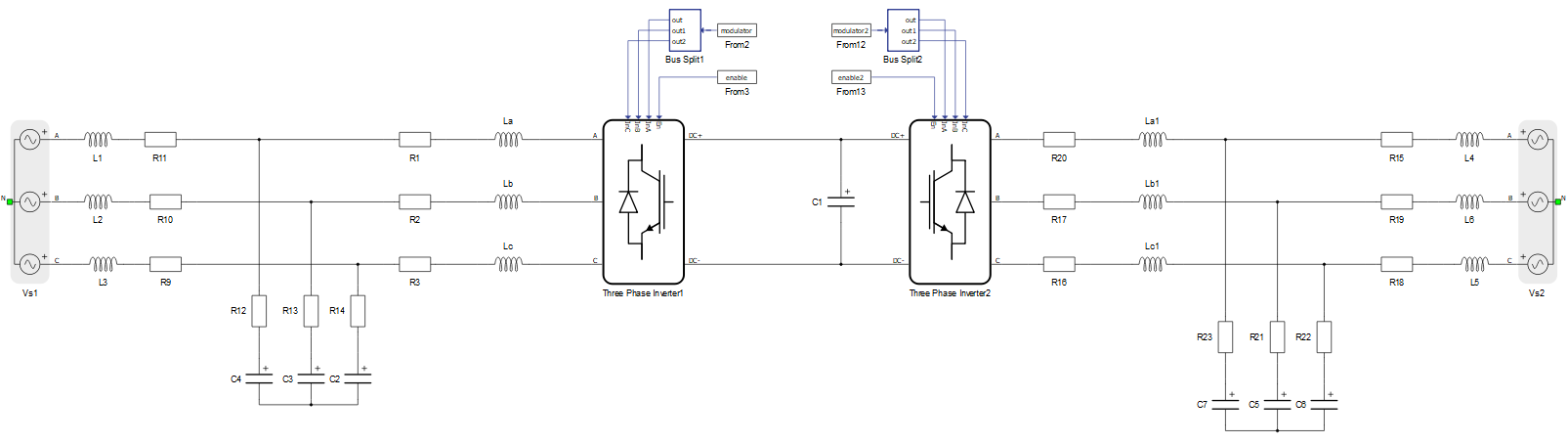

Another example where there are multiple converters in the model is a three phase back-to-back converter shown in Figure 3. The overall weight of converters in the model is 6. There is no HIL configuration that supports converters up to weight 6 per single core, thus circuit partitioning must be performed in this model.

Too many contactors in the circuit

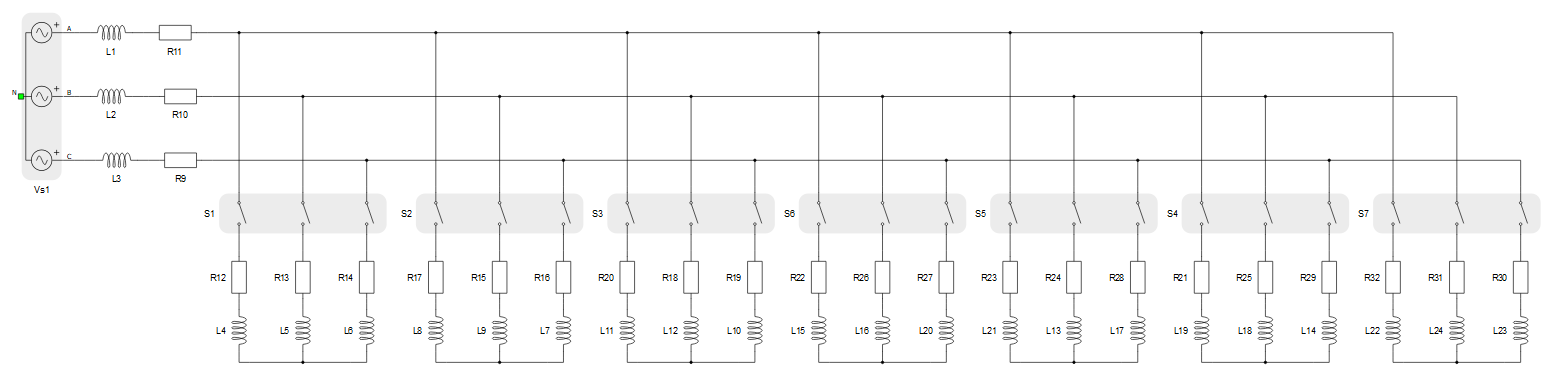

The number of ideal contactors supported per core is 6 for all device configurations. If the number of contactors exceeds this number, circuit partitioning is unavoidable. This case usually occurs in microgrid models where there are lot of protection devices and circuit breakers. An example of a model with 7 contactors is shown in Figure 4.

Matrix memory overload

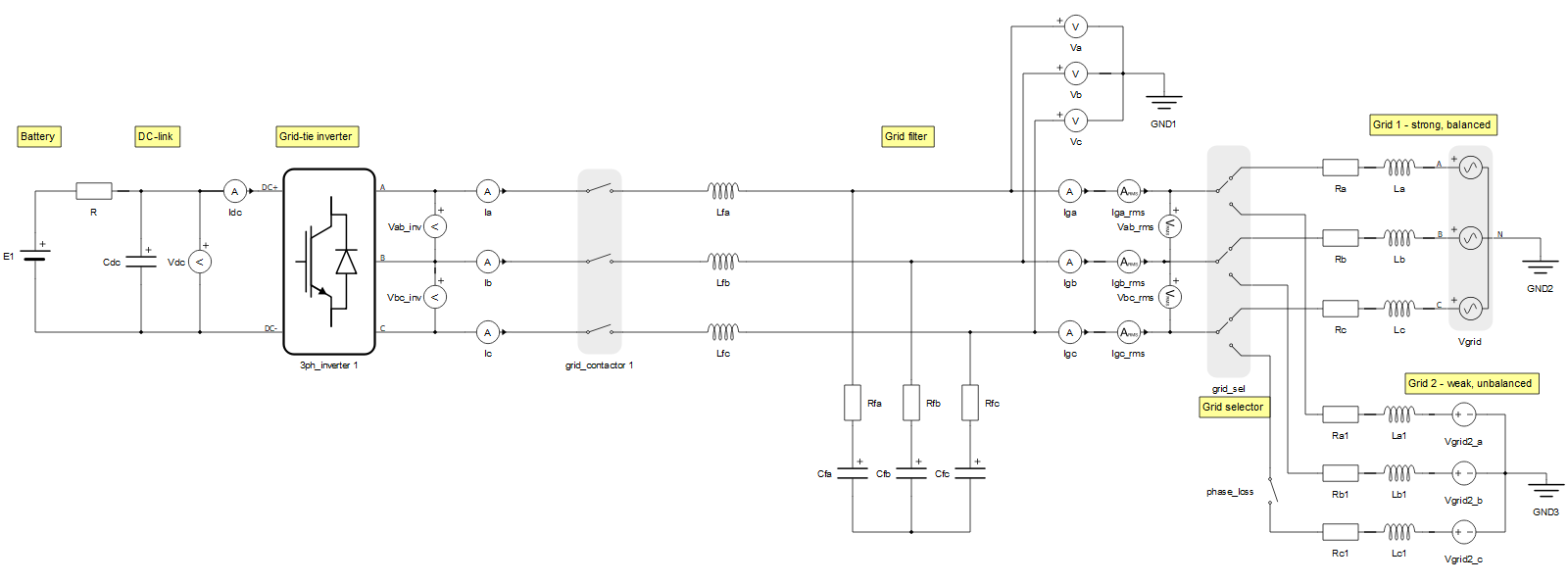

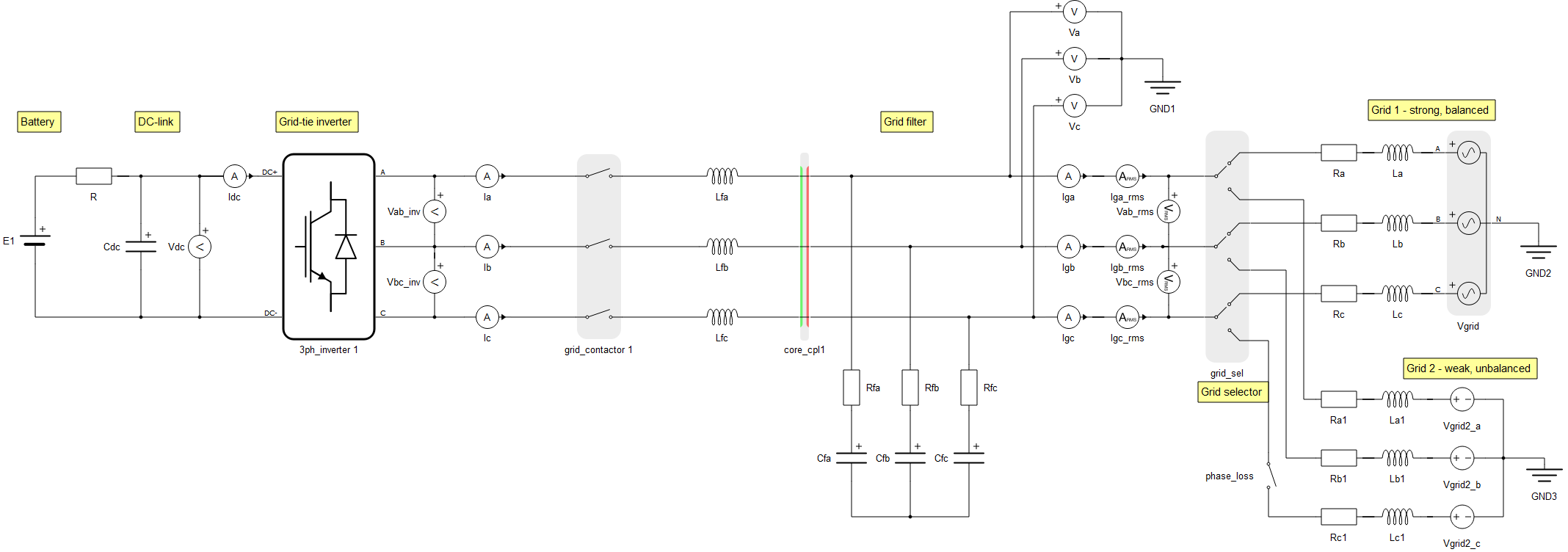

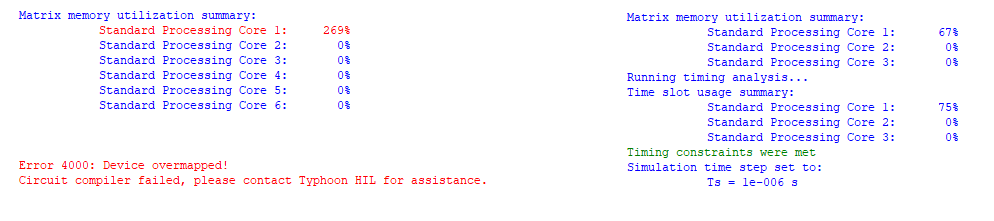

In the example shown in Figure 5, it seems that none of the hardware resource is overloaded – the number of contactors is less than 6, the overall weight of the converter is 3. However, if the model is compiled for HIL604 C1, an error message will be reported as shown on the left side of Figure 7, stating that the matrix memory utilization of core 1 is 269%. Partitioning the model as shown in Figure 6 is one way to solve this issue. This will result in a model that runs in two cores with a 1μs simulation time step. In this case, however, changing the HIL604 configuration to C4 will solve the problem without circuit partitioning. The compiler report for HIL604 C4 is shown on the right side of Figure 7.

Simulation time step too big

By partitioning the circuit the computation is distributed across multiple cores and/or devices and lower simulation rates can be achieved. This can be demonstrated by the IEEE 13 node bus example model in the Example Explorer. Currently this model runs with a fixed timestep of 4μs. If it would be partitioned in two cores, it would run at 1μs.