Irregular Model Example

Example of a model where circuit partitioning is needed to compile the model in real-time.

Real-time only: This document is valid only for real-time/VHIL

simulation.

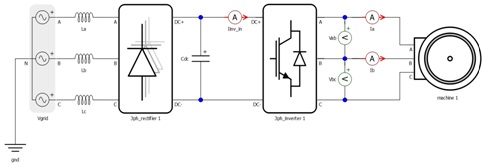

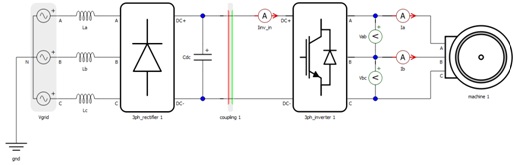

The model depicted in Figure 1 will fail to compile due to too high overall weight of converters in a single sub-circuit. The issue can be fixed by dividing the circuit into two sub-circuits where each sub-circuit holds only one converter as depicted in Figure 2.